Table of Contents Hide

What Is a CSP LED

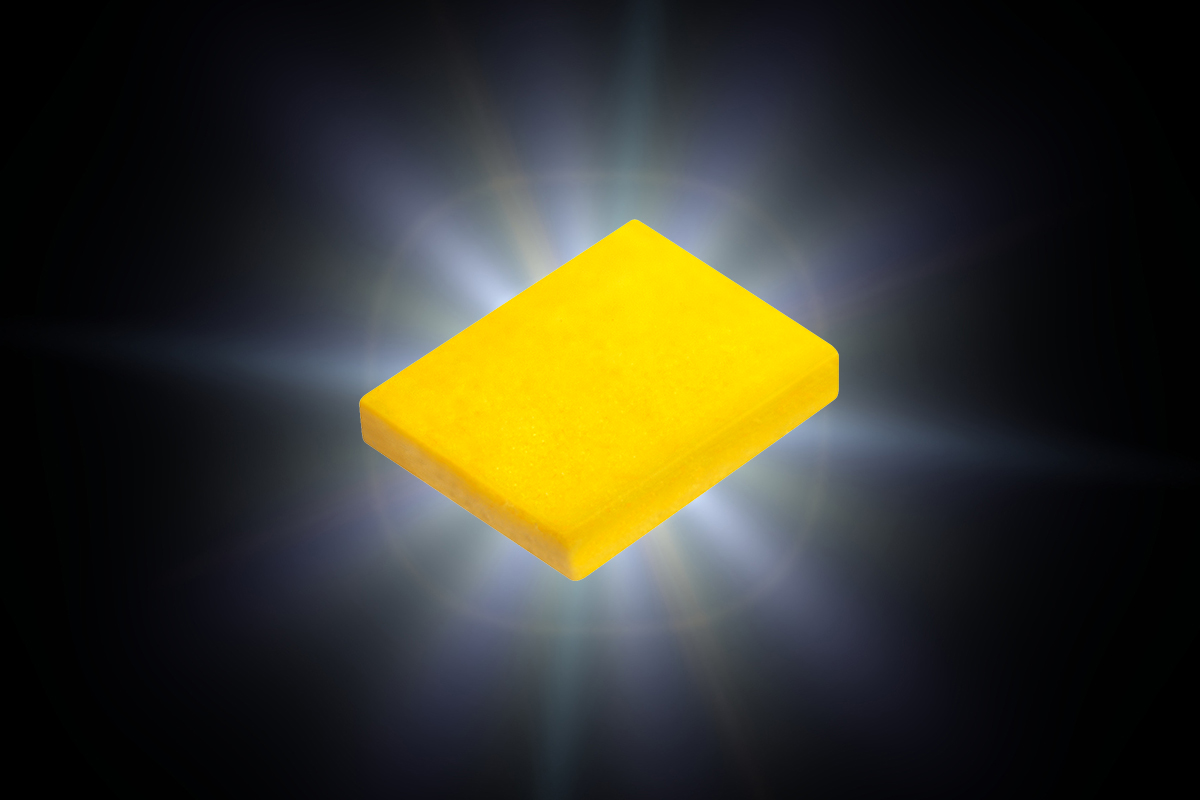

A chip scale package (CSP) LED is defined as an LED package that has a close ratio between the volume of the LED chip and the total volume of the LED package. A CSP package is essentially a bare LED die (chip) on which a phosphor layer is coated, with the underside of the die metallized with the P and N contacts to form the electrical connection and thermal path. In the semiconductor industry, a chip scale package was initially defined as a package with no more than 1.2 times the size of the chip. Soon the term CSP has been used to promote a miniature package that achieves its small footprint through design innovation. In the case of CSP LEDs, package miniaturization is achieved by eliminating the plastic submount or ceramic substrate found on a conventional mid-power or high power LED package.How LEDs Work

Light emitting diodes take advantage of the direct and wide bandgap of gallium nitride (GaN) to create electroluminescence. Gallium nitride is impregnated or doped with donor impurity atoms and acceptor impurity atoms to form an N-type semiconductor layer and a P-type semiconductor layer, respectively. These GaN layers are epitaxially grown on a carrier wafer (also called substrate) which is made of sapphire, silicon carbide (SiC), silicon (Si), or GaN. When a bias is applied across the doped layers, electrons from the conduction band of the n-type semiconductor layer and holes from the valence band of the p-type semiconductor layer flow toward the p-n junction which is sandwiched between two layers. The intracrystalline recombination of these holes and electrons releases energy in the form of photons, which are projected outwards as light. The short wavelength monochromatic light is then converted to broad-spectrum white light by a phosphor layer which is deposited over the LED chip.Conventional LED Architectures

As you can see, an LED package has three essential elements: GaN layers, a wafer that supports the epitaxial growth of the GaN layers, and a phosphor layer to down-convert part of the blue or other short wavelength emission from GaN LEDs in order to produce white light. However, in practical applications an LED package has a more complex architecture. Today the majority of LEDs are designed in surface-mount plastic leaded chip carrier (PLCC) packages. In this type of packages, the LED die is mounted on a silver (Ag)-plated metal lead frame. The lead frame sits in a plastic cavity formed by highly reflective material such as PPA, PCT or EMC. The positive and negative electrodes of the lead frame are wire bonded to the anode ohmic contact formed on the P-type GaN layer and the cathode ohmic contact formed on the n-type GaN layer, respectively. In high power LED packages, the LED die is mounted a metallized ceramic substrate which has positive and negative terminal pads on the bottom of the substrate. Wire bonding is needed to connect cathode of the junction to the negative terminal via an electrical interconnect layer. The substrate may have an array of thermal vias and a thermal pad on the underside that help improve the thermal performance.The Downsides of Overdesigned Packages

Conventional wire-bonded, submount-underlaid LED packages were overdesigned, which incurs a high package cost and introduces a number of parasitics. Packaging represents a significant portion in the typical cost breakdown of an LED package. In general, this cost element can constitute 60% of the total cost for high power LED packages and over 50% of the total cost for mid-power LED packages. The overdesigned architecture is accompanied by a large package form factor as well as increased lumen depreciation and color shift factors. The mid-power PLCC packages, in particular, are prone to accelerated lumen decay and color shift because the plastic housing has poor thermal and photo stability. The silver plated lead frame is susceptible to interaction with corrosive gases such as hydrogen sulfide (H2S) and may eventually lead to intermittent or open wire bond stitch. Wire bonding that connects electrodes of the chip to the lead frame also limits the packing and power density of the LED. Furthermore, a common open failure in conventional LEDs is often due to a broken wire bond.CSP LED Architecture

CSP LEDs are the latest incarnation of flip-chip LEDs which are designed to prevent light loss due to the mounting of electrode pad on the upside of P-type GaN layer while improving heat transfer efficiency and package reliability. In a flip-chip CSP LED, photons are pumped from the junction through the a light-transmissive wafer (substrate), instead of the P-type GaN layer as with the PLCC type mid-power LEDs and ceramic-based high power LEDs. The transparent wafer, N-type and P-type GaN layers grown on the wafer are flipped downward the bottom. In conventional LED architectures, the wafer is mounted on the plastic submount or ceramic substrate and faces upward. This design makes the wafer an obstructive element which blocks the electrical path to the electrodes and adds thermal resistance to the thermal path from the LED junction to a PCB.The epitaxial P-type GaN layer of a flip-chip CSP LED is the bottom layer which thermally and electrically interfaces the anode electrode on the underside of the CSP package. Electrical connection to the N-type GaN layer is made through the insulated, metal-deposited vias which pass through the P-type GaN layer and active layer. Chip scale packaging goes a step further by eliminating the submount that comes with flip-chip packages. The bottom surface of the flip-chip LED is exposed to allow solder connections to the anode and cathode electrodes. A conformal phosphor coating is applied directly onto flip-chip LED die, either just over the top surface of the wafer, or on all five facets of the chip.

Advantages of Chip Scale Packaging

The design of CSP LEDs drew on packaging know-how acquired by the semiconductor component industry to remove as many of the superfluous packaging elements as possible. CSP LEDs are also called package-free LEDs because the submount or package substrate are stripped out and no bonding wires are required, which translates to significantly reduced BOM cost. Wafer level packaging eliminates the need to go through a multitude of steps in a packaging line, allowing the processing cost to be cut down drastically. The technology scales down the size of an LED package to a size hardly larger than that of the LED die itself and thus saves considerable space.The advent of CSP LEDs has an epoch-making significance in the history of LED lighting, in particular when it comes to fact that the notoriously unreliable PLCC-type mid-power LEDs has been occupying a dominant market share for their cost advantage as compared with the ceramic-based high power LEDs. Mid-power LEDs can often exhibit more rapid lumen degradation and undergo more chromaticity shift mechanisms than high-power LEDs. This faster degradation in light output and color stability is largely due to the use of the plastic resin from which the LED housing is molded. Despite the use of epoxy mounting compound (EMC) which has relatively higher resistance to thermal degradation and photo oxidation, the most common polymer matrices used for molding reflective cavity are cheap polyphthalamide (PPA) and polycyclohexylenedimethylene terephthalate (PCT). These synthetic plastic resins will discolor at high temperatures, which not only leads to color shift in the blue direction, the reduced reflectivity due to resin discoloration and lead frame oxidation also substantially compromises luminous efficacy.

CSP LEDs make a lot of sense not just because the package-free design allows the cost savings from stripping of superfluous elements to be passed on to end-users. The excellent lumen maintenance, color stability and package reliability of CSP LEDs enable these low cost packages to deliver a more sustainable solution and a longer ROI than the spectrally short-lived, thermally unstable mid-power PLCC LEDs. The internal construction of mid-power PLCC packages includes a reflective cavity to prevent the otherwise leakage of light from the underside of transparent sapphire substrates. While CSP LEDs still require reflective coating of the bottom and sometimes side walls to redirect the scattered light toward the top, the flip-chip structure turns the transparent sapphire substrate into a light extraction window, rather than a light loss surface. This feature, combined with the direct thermal and electrical interfacing of with the N-type and P-type GaN layers with the bottom anode and cathode electrodes, allows CSP packages to completely remove the LED housing and lead frame assembly.

Removal of plastic submounts and lead frames results in the absence of one of PLCC-LED's dominant lumen depreciation and color shift factors in CSP packages. The wire-bonding-free design further contributes to the reliability and performance of CSP LEDs. Bonding wires that connect the lead frame to LED electrodes can break due to internal stress in the encapsulating resin, excessively large flows of electrical current, or electromigration. No bonding wire connections allow CSP LEDs to eliminate the risk factor of open circuit failures within the package. In CSP LEDs, the P-type GaN layer is in direct contact with the anode pad and the N-type GaN layer is connected to the cathode pad through metalized vias. This design reduces both the length of thermal path and the thermal resistance along the thermal path, which allows effective thermal management. Thermally efficient design and a robust electrical conduction path allow the LEDs to be driven at higher currents than conventional LED packages. As a result, CSP LEDs deliver high flux density in an ultra-compact form factor and redefine lumen maintenance, color stability and reliability.

Challenges

Although the advantages of the CSP approach are not in doubt, CSP LEDs aren't without their challenges. The flip-chip structure requires the top-mount wafer to have high optical transparency so that a good photon extraction efficiency can be achieved. The optical property of sapphire fits in with this specification, but this wafer material has a high dislocation density (13%) in the epitaxial films. High lattice mismatch to GaN results in a low internal quantum efficiency (IQE) that the LED industry has been struggling with. IQE improvement, however, is a universal challenge to the LED industry. To bring package features down into the chip level, wafer scale packaging is employed for today's CSP architectures. For LED packaging at this level, wafer configuration is critical to phosphor integration.Wafer level chip scale packaging (WLCSP) is typically used to produce surface emitters (light is emitted from the top surface, as opposed to volume emitters which produce emission from all five facets). In this process, phosphor coating is made on the entire epitaxial wafer before it is diced into individual CSP packages. Blue photons, however, will escape from the sidewalls of sapphire-based devices. This means implementing WLCSP on GaN-on-Sapphire flip-chip LEDs becomes a challenge as the epitaxial wafer has to be diced into individual dies to ensure good side wall coverage on the chip with phosphor dispensing. Chip binning is required to ensure minimal within-wafer pump wavelength variation across the individual dies before they're batch dispensed with phosphor.

To eliminate blue leak from wafers and further drive down the wafer cost, silicon has been introduced into WLCSP as a transitory wafer material. The silicon wafer is removed after the epitaxial growth is completed. Phosphor is coated as a film directly over the GaN layer. With this method, the problem of blue leak is addressed, and no additional steps such as chip dicing, binning and transferring are required. But the challenge comes from growing high quality GaN epilayers on silicon, which has 17% lattice mismatch and 54% CTE mismatch to GaN. High density threading dislocations due to lattice mismatch and cracking or bowing due to the thermal mismatch impede the use of cost competitive silicon wafers for mass production of GaN LEDs.

The major challenge to the LED industry at the package level is the fundamental Stokes losses which occur as blue photons are down converted to green and red photons. As a result, the overwhelming majority of the lighting products for interior lighting applications have a mediocre 80 CRI and a high color temperature. Faithful reproduction of colors to create a visually pleasing environment, and productive implementation of visually demanding tasks, including reading tasks, detail work and color-critical tasks all rely on a high CRI light source. Ever since the phase-out of 90+CRI incandescent lamps, the highly saturated colors of everything around us under artificial lighting are significantly distorted. The lighting industry continues to churn out poor color quality LED products with an extremely high correlated color temperature (CCT) for residential lighting applications. High CCT light contains a significant portion of blue in its light spectrum. People who are exposed to blue-rich spectrum light in the evening can have their circadian rhythms disrupted because a high dosage of blue will suppress the release of melatonin, a critical hormone that signals to the human body to prepare for a regenerative sleep. Circadian disruption affects cell metabolism and proliferation, and is linked to increased incidence of diseases in modern society.

Narrowing the full width half maximum (FWHM) bands for the red and green SPDs (spectral power distributions) thereby reducing Stokes loss is the key to elimination of the trade-off between luminous efficacy (or source efficiency) and color quality. The opportunity is thus to develop phosphors with narrower emission linewidths for high efficiency down-conversions. The use quantum dots (QDs) as narrow band down-converters offers an alternative approach.